### 10MSPS, 12-bit Analog Input Board for PCI

\* Specifications, color and design of the products are subject to change without notice.

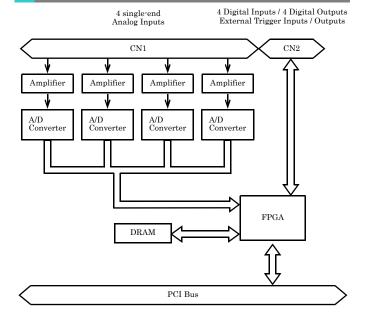

This product is a PCI bus-compliant interface board that expands the input function of a PC for analog signals.

Maximum conversion speed is 10MSPS (100nsec), with simultaneous sampling of four channels at a same time. The large (32M data) buffer memory and bus master transfer function allow continuous data acquisition to be performed at high speed for a long period.

Sampling can be started and stopped by software, conversion data comparison (level comparison, in-range comparison, out-of-range comparison), external trigger, or event controller output.

This product uses a BNC connector that can connect directly to the signal source.

Also features four digital input and output ports respectively (requires the optional DT-E3 cable).

You can use the driver library (API-PAC(W32)) supplied with the board to write Windows application programs in any programming language (such as Visual Basic, Visual C++, etc.) that supports the calling of Win32 API functions.

- \* The contents in this document are subject to change without notice.

- \* Visit the CONTEC website to check the latest details in the document.

- \* The information in the data sheets is as of July 2022.

### **Features**

# Maximum conversion speed is 10MSPS (100nsec), with simultaneous sampling of 4channels at a time

The maximum conversion speed is 10MSPS (100nsec) and 4channels can be sampled simultaneously.

The range for each channel can be set independently by software to match the level of the input signal source. (Input range:  $\pm 10V$ ,  $\pm 5V$ ,  $\pm 2.5V$ ,  $\pm 1.25V$  or  $0 - \pm 10V$ ,  $0 - \pm 5V$ ,  $0 - \pm 2.5V$ )Also features digital inputs and outputs (four LVTTL level input and output ports respectively). (requires the optional DT-E3 cable)

# Sampling can be controlled by software, conversion data comparison, external trigger, event controller output, and similar start and stop conditions

Sampling can be setup to be started and stopped by software, conversion data comparison, external trigger, or event controller output.

Control of sampling start and stop is completely independent and a separate setting is provided for each. It is also possible to specify that sampling stop after a specified number of samples.

The conversion data comparison function can perform level, in-range, and out-of-range comparisons on the conversion data

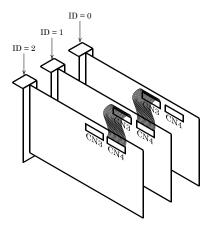

# Incorporates a synchronization control connector for synchronized operation

A synchronization control connector is provided for synchronized control of up to 16 boards. This means the number of channels can be increased simply by adding boards. It is also easy to synchronize operation with other CONTEC boards that have a synchronization control connector.

# Large (32M data) buffer memory and bus master transfer function allow continuous data acquisition at high speed for a long period.

The large (32M data) buffer memory and bus master transfer function allow continuous data acquisition to be performed at high speed for a long period. The bus master transfer function allows large volumes of data to be transferred between the board and PC without loading the CPU.

### BNC connector used for analog input pin

The BNC connector used for the analog input has a characteristic impedance of  $50\Omega$  and is of a type commonly used for high speed analog signal.

This makes it easy to connect to other devices with a BNC connector.

### Termination resistor selection function

A  $50\Omega$  termination resistor can be set to minimize the distortion caused by the reflection of high-speed input signals. The input range cannot be set to ±10V or 0 to +10V when the termination resistor is used.

# Digital filter function included to prevent misdetection due to chattering on external input signals

A digital filter is included to prevent misdetection due to chattering on the digital input signals.

#### Software-based calibration function

Calibration of analog input can be all performed by software. Apart from the adjustment information prepared before shipment, additional adjustment information can be stored according to the use environment.

### Windows compatible driver libraries are attached.

Using the attached driver library API-PAC(W32) makes it possible to create applications of Window. In addition, a diagnostic program by which the operations of hardware can be checked is provided.

### **Specification**

| Ana   | Item                                                                                                                                                                                                                                                                                                              | Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|       | alog input                                                                                                                                                                                                                                                                                                        | · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|       | Isolated specification                                                                                                                                                                                                                                                                                            | Unisolated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|       | Туре                                                                                                                                                                                                                                                                                                              | Single-Ended Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|       | Number of input channels                                                                                                                                                                                                                                                                                          | 4channels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|       | Input range                                                                                                                                                                                                                                                                                                       | (when $50\Omega$ termination setting disabled)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|       |                                                                                                                                                                                                                                                                                                                   | Bipolar ±10V, ±5V, ±2.5V, ±1.25V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|       |                                                                                                                                                                                                                                                                                                                   | or Unipolar 0 - +10V, 0 - +5V, 0 - +2.5V<br>(when 50Ω termination setting enabled)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|       |                                                                                                                                                                                                                                                                                                                   | Bipolar ±5V, ±2.5V, ±1.25V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|       |                                                                                                                                                                                                                                                                                                                   | or Unipolar 0 - +5V, 0 - +2.5V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|       | Absolute max. input                                                                                                                                                                                                                                                                                               | (when 50Ω termination setting disabled)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|       | voltage *1                                                                                                                                                                                                                                                                                                        | When the power is ON ±13V (Max.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|       |                                                                                                                                                                                                                                                                                                                   | When the power is OFF $\pm 13V$ (Max.) (when $50\Omega$ termination setting enabled)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|       |                                                                                                                                                                                                                                                                                                                   | When the power is ON ±7V (Max.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|       |                                                                                                                                                                                                                                                                                                                   | When the power is OFF ±7V (Max.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|       | Input impedance                                                                                                                                                                                                                                                                                                   | 1M $\Omega$ or more                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|       |                                                                                                                                                                                                                                                                                                                   | $50\Omega\pm1\%$ (when $50\Omega$ termination setting enabled)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|       | Resolution                                                                                                                                                                                                                                                                                                        | 12bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|       | Conversion accuracy *2*4                                                                                                                                                                                                                                                                                          | Within ±4LSB (input range : ±10V) Within ±6LSB (input range : 0 - +10V, ±5V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|       | 2 4                                                                                                                                                                                                                                                                                                               | Within ±8LSB (input range : 0 - +10V, ±5V)  Within ±8LSB (input range : 0 - +5V, ±2.5V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|       |                                                                                                                                                                                                                                                                                                                   | Within ±10LSB (input range : 0 - +2.5V, ±1.25V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|       | Non-Linearity error                                                                                                                                                                                                                                                                                               | Within ±3LSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|       | *2*3*4                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|       | Conversion speed                                                                                                                                                                                                                                                                                                  | 100nsec (Max.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|       | Passband (-3dB)                                                                                                                                                                                                                                                                                                   | 10MHz<br>32M data (Max.) *5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|       | Buffer memory Conversion start trigger                                                                                                                                                                                                                                                                            | Software, conversion data compare, external trigger, and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|       | Conversion start trigger                                                                                                                                                                                                                                                                                          | event controller output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|       | Conversion stop trigger                                                                                                                                                                                                                                                                                           | Settings include data save complete, conversion data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|       |                                                                                                                                                                                                                                                                                                                   | compare,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|       | External start simus                                                                                                                                                                                                                                                                                              | external trigger, event controller output, and software.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|       | External start signal                                                                                                                                                                                                                                                                                             | LVTTL level (Rising or falling edge can be selected by software)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|       | External stop signal                                                                                                                                                                                                                                                                                              | LVTTL level (Rising or falling edge can be selected by                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|       |                                                                                                                                                                                                                                                                                                                   | software)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|       | External clock signal                                                                                                                                                                                                                                                                                             | LVTTL level (Rising or falling edge can be selected by software)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|       | External status output                                                                                                                                                                                                                                                                                            | LVTTL level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|       | signal                                                                                                                                                                                                                                                                                                            | Sampling clock output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| Digit | tal I/O                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|       | Number of input channels                                                                                                                                                                                                                                                                                          | Unisolated input 4channels (LVTTL level positive logic)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|       | Number of output                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|       | channels                                                                                                                                                                                                                                                                                                          | Unisolated output 4channels (LVTTL level positive logic)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|       | master section                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| Bus   |                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| Bus   | DMA channels                                                                                                                                                                                                                                                                                                      | 1channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| Bus   | DMA channels<br>Transfer bus width                                                                                                                                                                                                                                                                                | 32bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| Bus   | DMA channels Transfer bus width Transfer data length                                                                                                                                                                                                                                                              | 32bit<br>8 PCI data length (Max.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| Bus   | DMA channels Transfer bus width Transfer data length FIFO                                                                                                                                                                                                                                                         | 32bit<br>8 PCI data length (Max.)<br>1K data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| Bus   | DMA channels Transfer bus width Transfer data length                                                                                                                                                                                                                                                              | 32bit<br>8 PCI data length (Max.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|       | DMA channels Transfer bus width Transfer data length FIFO Scatter/Gather function chronization bus section                                                                                                                                                                                                        | 32bit<br>8 PCI data length (Max.)<br>1K data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|       | DMA channels Transfer bus width Transfer data length FIFO Scatter/Gather function                                                                                                                                                                                                                                 | 32bit 8 PCI data length (Max.) 1K data 64M-Byte  Selection of output signal with the software when specifying a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|       | DMA channels Transfer bus width Transfer data length FIFO Scatter/Gather function chronization bus section Control output signal                                                                                                                                                                                  | 32bit 8 PCI data length (Max.) 1K data 64M-Byte  Selection of output signal with the software when specifying a sync master board.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|       | DMA channels Transfer bus width Transfer data length FIFO Scatter/Gather function chronization bus section                                                                                                                                                                                                        | 32bit 8 PCI data length (Max.) 1K data 64M-Byte  Selection of output signal with the software when specifying a sync master board. Selection of sync factor with the software when specifying                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|       | DMA channels Transfer bus width Transfer data length FIFO Scatter/Gather function chronization bus section Control output signal                                                                                                                                                                                  | 32bit 8 PCI data length (Max.) 1K data 64M-Byte  Selection of output signal with the software when specifying a sync master board. Selection of sync factor with the software when specifying sync slave boards.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|       | DMA channels Transfer bus width Transfer data length FIFO Scatter/Gather function chronization bus section Control output signal                                                                                                                                                                                  | 32bit 8 PCI data length (Max.) 1K data 64M-Byte  Selection of output signal with the software when specifying a sync master board. Selection of sync factor with the software when specifying                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|       | DMA channels Transfer bus width Transfer data length FIFO Scatter/Gather function chronization bus section Control output signal  Control input signal  Max. board count for connection Connector (CN3,                                                                                                           | 32bit 8 PCI data length (Max.) 1K data 64M-Byte  Selection of output signal with the software when specifying a sync master board. Selection of sync factor with the software when specifying sync slave boards.  16 boards including the master board                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| Syne  | DMA channels Transfer bus width Transfer data length FIFO Scatter/Gather function chronization bus section Control output signal Control input signal Max. board count for connection Connector (CN3, CN4)                                                                                                        | 32bit 8 PCI data length (Max.) 1K data 64M-Byte  Selection of output signal with the software when specifying a sync master board. Selection of sync factor with the software when specifying sync slave boards.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| Syne  | DMA channels Transfer bus width Transfer data length FIFO Scatter/Gather function Control output signal  Control input signal  Max. board count for connection Connector (CN3, CN4)                                                                                                                               | 32bit 8 PCI data length (Max.) 1K data 64M-Byte  Selection of output signal with the software when specifying a sync master board. Selection of sync factor with the software when specifying sync slave boards.  16 boards including the master board  PS-10PE-D4T1-B1 equivalent (mfd. By JAE) x 2                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| Syne  | DMA channels Transfer bus width Transfer data length FIFO Scatter/Gather function chronization bus section Control output signal  Control input signal  Max. board count for connection Connector (CN3, CN4)                                                                                                      | 32bit 8 PCI data length (Max.) 1K data 64M-Byte  Selection of output signal with the software when specifying a sync master board. Selection of sync factor with the software when specifying sync slave boards.  16 boards including the master board PS-10PE-D4T1-B1 equivalent (mfd. By JAE) x 2  64 ports x 1,256 ports x 1 region                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| Syne  | DMA channels Transfer bus width Transfer data length FIFO Scatter/Gather function Control output signal  Control input signal  Max. board count for connection Connector (CN3, CN4)                                                                                                                               | 32bit 8 PCI data length (Max.) 1K data 64M-Byte  Selection of output signal with the software when specifying a sync master board. Selection of sync factor with the software when specifying sync slave boards.  16 boards including the master board  PS-10PE-D4T1-B1 equivalent (mfd. By JAE) x 2                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| Syne  | DMA channels Transfer bus width Transfer data length FIFO Scatter/Gather function chronization bus section Control output signal  Max. board count for connection Connector (CN3, CN4)  mmon I/O address Interrupt level                                                                                          | 32bit 8 PCI data length (Max.) 1K data 64M-Byte  Selection of output signal with the software when specifying a sync master board. Selection of sync factor with the software when specifying sync slave boards. 16 boards including the master board  PS-10PE-D4T1-B1 equivalent (mfd. By JAE) x 2  64 ports x 1,256 ports x 1 region Errors and various factors, One interrupt request line as INTA For analog (CN1): BNC connector DB-414K equivalent [mfd. By INSERT ENTERPRISE],                                                                                                                                                                               |  |  |  |  |

| Syne  | DMA channels Transfer bus width Transfer data length FIFO Scatter/Gather function chronization bus section Control output signal  Max. board count for connection Connector (CN3, CN4) IMMO I/O address Interrupt level Connector used                                                                            | 32bit 8 PCI data length (Max.) 1K data 64M-Byte  Selection of output signal with the software when specifying a sync master board. Selection of sync factor with the software when specifying sync slave boards. 16 boards including the master board  PS-10PE-D4T1-B1 equivalent (mfd. By JAE) x 2  64 ports x 1,256 ports x 1 region Errors and various factors, One interrupt request line as INTA For analog (CN1): BNC connector DB-414K equivalent [mfd. By INSERT ENTERPRISE], For digital (CN2): 16pin pin header connector                                                                                                                                 |  |  |  |  |

| Syne  | DMA channels Transfer bus width Transfer data length FIFO Scatter/Gather function chronization bus section Control output signal  Control input signal  Max. board count for connection Connector (CN3, CN4) Inmon I/O address Interrupt level Connector used                                                     | 32bit 8 PCI data length (Max.) 1K data 64M-Byte  Selection of output signal with the software when specifying a sync master board. Selection of sync factor with the software when specifying sync slave boards.  16 boards including the master board  PS-10PE-D4T1-B1 equivalent (mfd. By JAE) x 2  64 ports x 1,256 ports x 1 region Errors and various factors, One interrupt request line as INTA For analog (CN1): BNC connector DB-414K equivalent [mfd. By INSERT ENTERPRISE], For digital (CN2): 16pin pin header connector 5VDC 2500mA (Max.)                                                                                                             |  |  |  |  |

| Syne  | DMA channels Transfer bus width Transfer data length FIFO Scatter/Gather function chronization bus section Control output signal  Max. board count for connection Connector (CN3, CN4)  mmon I/O address Interrupt level Connector used                                                                           | 32bit 8 PCI data length (Max.) 1K data 64M-Byte  Selection of output signal with the software when specifying a sync master board. Selection of sync factor with the software when specifying sync slave boards.  16 boards including the master board  PS-10PE-D4T1-B1 equivalent (mfd. By JAE) x 2  64 ports x 1,256 ports x 1 region  Errors and various factors, One interrupt request line as INTA For analog (CN1): BNC connector DB-414K equivalent [mfd. By INSERT ENTERPRISE], For digital (CN2): 16pin pin header connector  5VDC 2500mA (Max.) 0 - 50°C, 10 - 90%RH (No condensation)                                                                    |  |  |  |  |

| Syne  | DMA channels Transfer bus width Transfer data length FIFO Scatter/Gather function chronization bus section Control output signal  Control input signal  Max. board count for connection Connector (CN3, CN4) Inmon I/O address Interrupt level Connector used                                                     | 32bit 8 PCI data length (Max.) 1K data 64M-Byte  Selection of output signal with the software when specifying a sync master board. Selection of sync factor with the software when specifying sync slave boards.  16 boards including the master board  PS-10PE-D4T1-B1 equivalent (mfd. By JAE) x 2  64 ports x 1,256 ports x 1 region Errors and various factors, One interrupt request line as INTA For analog (CN1): BNC connector DB-414K equivalent [mfd. By INSERT ENTERPRISE], For digital (CN2): 16pin pin header connector 5VDC 2500mA (Max.)                                                                                                             |  |  |  |  |

| Syne  | DMA channels Transfer bus width Transfer data length FIFO Scatter/Gather function chronization bus section Control output signal  Max. board count for connection Connector (CN3, CN4) mmon I/O address Interrupt level Connector used                                                                            | 32bit 8 PCI data length (Max.) 1K data 64M-Byte  Selection of output signal with the software when specifying a sync master board. Selection of sync factor with the software when specifying sync slave boards.  16 boards including the master board PS-10PE-D4T1-B1 equivalent (mfd. By JAE) x 2  64 ports x 1,256 ports x 1 region Errors and various factors, One interrupt request line as INTA For analog (CN1): BNC connector DB-414K equivalent [mfd. By INSERT ENTERPRISE], For digital (CN2): 16pin pin header connector 5VDC 2500mA (Max.) 0 - 50°C, 10 - 90%RH (No condensation) 32bit, 33MHz, Universal key shapes supported *6                       |  |  |  |  |

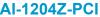

| Syne  | DMA channels Transfer bus width Transfer data length FIFO Scatter/Gather function chronization bus section Control output signal  Max. board count for connection Connector (CN3, CN4) mon I/O address Interrupt level Connector used  Currrent consumption Operating condition Bus specification Dimensions (mm) | 32bit 8 PCI data length (Max.) 1K data 64M-Byte  Selection of output signal with the software when specifying a sync master board. Selection of sync factor with the software when specifying sync slave boards. 16 boards including the master board  PS-10PE-D4T1-B1 equivalent (mfd. By JAE) x 2  64 ports x 1,256 ports x 1 region Errors and various factors, One interrupt request line as INTA For analog (CN1): BNC connector DB-414K equivalent [mfd. By INSERT ENTERPRISE], For digital (CN2): 16pin pin header connector 5VDC 2500mA (Max.) 0 - 50°C, 10 - 90%RH (No condensation) 32bit, 33MHz, Universal key shapes supported *6 176.41(L) x 105.68(H) |  |  |  |  |

- Do not input voltages in excess of the maximum input voltage. Similarly, do not input voltage exceeding 1.5 times the range being used, even if less than the maximum input voltage. Inputting too high a voltage may cause a fault.

- The rated precision may not be achieved depending on the cable used.

The non-linearity error means an error of approximately 0.1% occurs over the maximum range at 0°C and 50°C ambient temperature.

- A R6161[ADVANTEST] voltage generator was used for measurements.

- The initial value of the buffer memory is 500K data. Refer to the driver software help for information on how to change the memory size and configurable range. Depending on the OS and PC configuration used, it may not be possible to set the buffer memory to the

- maximum capacity.

This product requires +5V power supply from expansion slots (it does not operate in the environment of only +3.3V power supply).

#### **Board Dimensions**

### **Support Software**

### Windows version of analog I/O driver API-AIO(WDM)

The API-AIO(WDM) is the Windows version driver library software that provides products in the form of Win32 API functions (DLL). Various sample programs such as Visual Basic and Visual C++, etc and diagnostic program \*1useful for checking operation is provided.

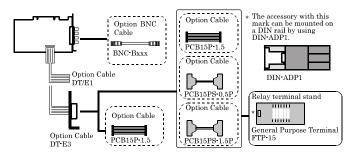

### **Cable & Connector**

### Cable(Option)

< For analog I/O >

**BNC Cable** : BNC-B100 (1m)

: BNC-B200 (2m)

: BNC-B300 (3m)

< For digital I/O >

Conversion Cable (16-Pin to 15-Pin) with Bracket (150mm)

: DT-E3

Flat Cable with 1 Sided 16-Pin Header Connector (1.5m)

: DT/E1

Shielded Cable with Connector on both sides

: PCB15PS-1.5P (1.5m) \*1\*2 for 15-pin D-Type Connector

DT-E3 is required.

It is required only when FTP-15 is used.

### **Accessories**

### **Accessories (Option)**

General Purpose Terminal (M3 x 15P): FTP-15 \*1

- DT-E3 and PCB15P-1.5 optional cable is required separately.

- Check the CONTEC's Web site for more information on these options.

### **Packing List**

Board [AI-1204Z-PCI] ...1 First step guide ... 1 CD-ROM \*1 [API-PAC(W32)] ...1 Synchronization control cable (10cm) ...1

\*1 The CD-ROM contains the driver software and User's Guide.

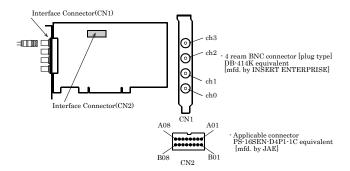

### How to connect the connectors

### **Connector shape**

To connect an external device to this product, plug the cable from the device into the interface connector (CN1, CN2) shown below.

This product has two interface connectors: the (CN1, BNC connector) for analog inputs and the (CN2, 16-pin pin-header connector) for digital inputs/outputs.

\* Please refer to chapter 1 for more information on the supported cable and accessories.

\* Please refer to page 2 for more information on the supported cable and accessories.

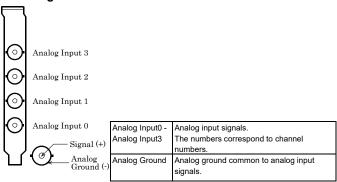

# Connector Pin Assignment Pin Assignment of CN1

### $\triangle$ CAUTION

If analog and digital ground are shorted together, noise on the digital signals may affect the analog signals. Accordingly, analog and digital ground should be separated.

### Pin Assignment of CN2

|  | CN2<br>A08 A01 | A01 | Digital Output 0            | B01 | Digital Output 1              |  |  |

|--|----------------|-----|-----------------------------|-----|-------------------------------|--|--|

|  |                | A02 | Digital Output 2            | B02 | Digital Output 3              |  |  |

|  |                | A03 | Digital Ground              | B03 | Digital Input 0               |  |  |

|  |                | A04 | Digital Input 1             | B04 | Digital Input 2               |  |  |

|  |                | A05 | Digital Input 3             | B05 | External Start Trigger Input  |  |  |

|  |                | A06 | External Stop Trigger Input | B06 | External Sampling Clock Input |  |  |

|  |                | A07 | Al Status Output            | B07 | Digital Ground                |  |  |

|  |                | 80A | N.C.                        | B08 | N.C.                          |  |  |

| Digital Input 0 - Digital Input 3 | Digital input signal.                                       |

|-----------------------------------|-------------------------------------------------------------|

| Digital Out 0 - Digital Output 3  | Digital output signal.                                      |

| External Start Trigger Input      | External trigger input signal for sampling start conditions |

| External Stop Trigger Input       | External trigger input signal for sampling stop conditions  |

| External Sampling Clock Input     | External sampling clock input signal                        |

| Al Status Output                  | Output the status signal.                                   |

| Digital Ground                    | Digital ground common to the each signal.                   |

| N.C.                              | No connection to this pin.                                  |

### **⚠** CAUTION

Do not connect any of the outputs to the analog or digital ground.

Neither connect outputs to each other. Doing either can result in a fault.

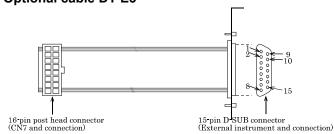

### **Optional cable DT-E3**

| Digital Output 0               | 1 |    | \$\$00000<br>\$\$00000<br>\$ | 3€ 10<br>0<br>0<br>0<br>0<br>0 | 9  | Digital Output 1                 |

|--------------------------------|---|----|------------------------------|--------------------------------|----|----------------------------------|

| Digital Output 2               | 2 | 1. |                              |                                | 10 | Digital Output 3                 |

| Digital Ground                 | 3 | 2  |                              |                                | 11 | Digital Input 0                  |

| Digital Input 1                | 4 | 8_ |                              |                                | 12 | Digital Input 2                  |

| Digital Input 3                | 5 |    |                              |                                | 13 | External Start Trigger<br>Input  |

| External Stop Trigger<br>Input | 6 |    |                              |                                |    | External Sampling Clock<br>Input |

| Al Status Output               | 7 |    |                              |                                | 15 | Digital Ground                   |

| Reserved                       | 8 |    |                              |                                |    |                                  |

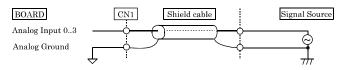

### **Analog Input Signal Connection**

### Single-ended Input

The following figure shows an example of shielded cable connection. For the CN1 each analog input, connect the core wire to the signal line and connect the shielding to ground.

### ⚠ CAUTION

- Do not touch the external connector (BNC connector) when the power is on. Otherwise this may malfunction, cause a failure due to static electricity.

- If the signal source contains over 5MHz signals, the signal may effect the cross-talk noise between channels.

- If this product and the signal source receive noise or the distance between this product and the signal source is too long, data may not be input properly.

The analog signal to be input should not exceed the maximum input voltage (based on this product analog ground). If it exceeds the maximum voltage, this product may be damaged.

- Input data remains indeterminate when no input pin is connected. The input pin for the channel not connected to the signal source must be connected to the analog ground.

- An input pin may fail to obtain input data normally when the signal source connected to the pin has high output impedance. If this is the case, change the signal source to one with lower output impedance or insert a high-speed amplifier buffer between the signal source and the analog input board to reduce the effect.

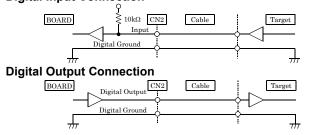

# Digital I/O signals and Control signals Connections

This section shows an example of how to connect digital I/O signals and the control signals(external trigger input signals and sampling clock input signal) using flat cable.

User can use an optional cable (DT/E1) or 15-pin D-SUB connector with bracket (DT-E3)and to connect your external devices to CN2.

Pulse (width: about 50nsec) synchronized with internal sampling clock is output to the Al Status Output pin. However, if the sampling clock setting is set to the external sampling clock input, level "L" is always output.

Al Status Output pin is an output in positive logic. All the digital I/O signals and control signals are LVTTL level signals.

### **Digital Input Connection**

### ⚠ CAUTION

Do not connect any output signal to the analog or digital ground. Do not interconnect outputs. Doing either can cause a malfunction.

If connected to each output, a pull-up resistor must be about 10 k $\Omega$  to pull up with a 3.3V power source.

Each input accepts 5V TTL signals.

### **Synchronization Control Connectors**

### **SC Connectors**

Controlling simultaneous operations between boards or controlling in sync with events is in part dependent on software performance. In order to enhance the reliability of the entire system and to solve these problems, the board is equipped with SC (Synchronization Control) connectors.

Connecting the SC connectors allows boards of the same or different models to operate in sync with one another. From the boards connected with the SC cable, select one master board and use others as slaves. On the master board, set the signal to be supplied to the slave boards with the software. On the slave boards, the signal from the master board can be set to either the pacer clock operation start or stop factor.

All board operations can also be stopped with a stop request from the master in case of an error, for example, or when requested from a slave board. A maximum of 16 boards can be connected including the master.

For more information on the setup procedure, see the driver software online help.

## Example 1: When clock start and stop requirements are set the same for multiple boards